# ADA4870ARR-EBZ User Guide

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

### **Evaluating the ADA4870 High Speed, High Output Current Amplifier**

### **FEATURES**

Enables easy evaluation of the ADA4870 Single-supply or dual-supply operation Robust thermal management

### **APPLICATIONS**

Organic light-emitting diode (OLED) panel driver

Active matrix organic light-emitting diode (AMOLED)

panel driver

Base transceiver station (RTS) envelope tracking

Base transceiver station (BTS) envelope tracking

Power field effect transistor (FET) driver

Ultrasound

Piezoelectric driver

PIN diode driver

Waveform generation

Automatic test equipment (ATE)

Charge-coupled device (CCD) panel driver

### **GENERAL DESCRIPTION**

The ADA4870 is a 40 V, unity-gain stable, high speed current feedback amplifier capable of delivering 1 A of output current from a 40 V supply. Manufactured using the Analog Devices, Inc., proprietary high voltage XFCB process, the innovative architecture of the ADA4870 enables high output power, high speed signal processing solutions in a variety of demanding applications.

The ADA4870 is ideal for driving high voltage power FETs, piezoelectric transducers, PIN diodes, and a variety of other demanding applications that require high speed from high supply voltage and high current output.

The ADA4870 is available in a power SOIC package (PSOP\_3) featuring an exposed thermal slug that provides high thermal conductivity to the printed circuit board (PCB) and heat sink enabling efficient heat transfer for improved reliability in demanding environments. The ADA4870 operates over the industrial temperature range of -40°C to +85°C.

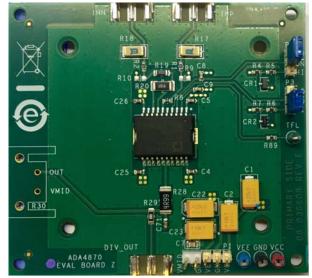

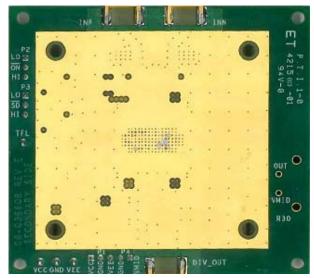

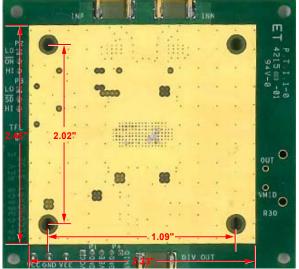

The ADA4870ARR-EBZ evaluation board provides a platform for quick and easy evaluation of the ADA4870. Figure 1 shows the top side of the evaluation board. Figure 2 shows the bottom side of the board with the large exposed copper area for applying a heat sink as needed.

Figure 1. Evaluation Board, Top Side

Figure 2. Evaluation Board, Bottom Side

2271-002

## **TABLE OF CONTENTS**

| reatures                                   | I |

|--------------------------------------------|---|

| Applications                               | 1 |

| General Description                        | 1 |

| Revision History                           | 2 |

| Evaluation Board Hardware                  | 3 |

| Board Stack Up                             | 3 |

| Power Supplies and Decoupling              | 3 |

| Input and Output                           | 3 |

| Symmetrical Supplies and DC-Coupled Inputs | 3 |

|                                            |   |

|   | Asymmetrical Supplies and Mild Supply Blas (VMID) | ••• |

|---|---------------------------------------------------|-----|

|   | ON, Initial Power-Up, and Short Circuit           | !   |

|   | Shutdown (SD)                                     |     |

|   | Thermal Monitor/Short-Circuit Flag (TFL)          | !   |

|   | Thermal Design and Heat Sink Selection            |     |

|   | Thermal Performance                               |     |

| E | valuation Board Schematic                         |     |

|   | ill of Matariala                                  |     |

### **REVISION HISTORY**

### 6/2016—Rev. 0 to Rev. A

| Changes to Applications Section, Figure 1, and Figure 2  | l  |

|----------------------------------------------------------|----|

| Changes to Board Stack Up Section, Power Supplies and    |    |

| Decoupling Section, and Input and Output Section         | 3  |

| Added Symmetrical Supplies and DC-Coupled Inputs Section |    |

| and Figure 3; Renumbered Sequentially                    | 3  |

| Added Asymmetrical Supplies and Mid Supply Bias (VMID)   |    |

| Section, Figure 4, and Figure 5                          | ŀ  |

| Changes to Table 1                                       | Į. |

| Changes to ON, Initial Power-Up, Short Circuit Section,  |    |

| Shutdown (SD) Section, and Thermal Design and            |    |

| Heat Sink Section5                                       | 5  |

| Added Figure 65                                          | 5  |

| Added Figure 76                                          | ó  |

| Changes to Thermal Performance Section, Figure 8, and    |    |

| Figure 9                                                 | ó  |

| Changes to Figure 10                                     | 7  |

| Changes to Table 2                                       | 3  |

6/2014—Revision 0: Initial Version

# EVALUATION BOARD HARDWARE BOARD STACK UP

The ADA4870ARR-EBZ evaluation board is a 6-layer board. All signal routing is on the top layer; the bottom layer is an exposed copper ground plane to facilitate the use of a heat sink. The heat sink is needed for high power dissipation projects, such as driving a 20  $\Omega$  load with the maximum output swing. The internal layers (Layer 2 through Layer 5) consist of the GND, VCC, VMID, and VEE planes.

### **POWER SUPPLIES AND DECOUPLING**

The evaluation board can be powered using a single supply or dual supplies. The total supply voltage ( $V_{\rm CC}-V_{EE}$ ) must be between 10 V and 40 V. The board provides sufficient power supply decoupling for high current, fast slewing signals with 22  $\mu F$  and 10  $\mu F$  tantalum capacitors installed at C1 and C2 where the  $V_{\rm CC}$  supply voltage is applied to the board; 22  $\mu F$  and 10  $\mu F$  tantalum capacitors are installed at C22 and C23 where the  $V_{EE}$  supply voltage is applied to the board. In addition, 0.1  $\mu F$  ceramic chip capacitors (C4 and C5) are placed in close proximity to the VCC pins (Pin 1, Pin 18, Pin 19, and Pin 20). And 0.1  $\mu F$  ceramic chip capacitors (C25 and C26) are placed in close proximity to the VEE pins (Pin 10, Pin 11, Pin 12, and Pin 13).

#### INPUT AND OUTPUT

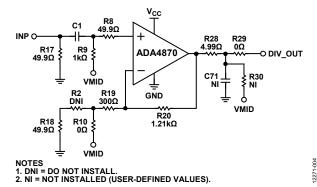

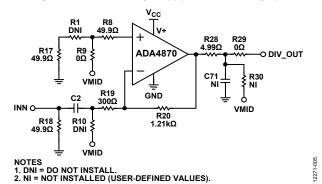

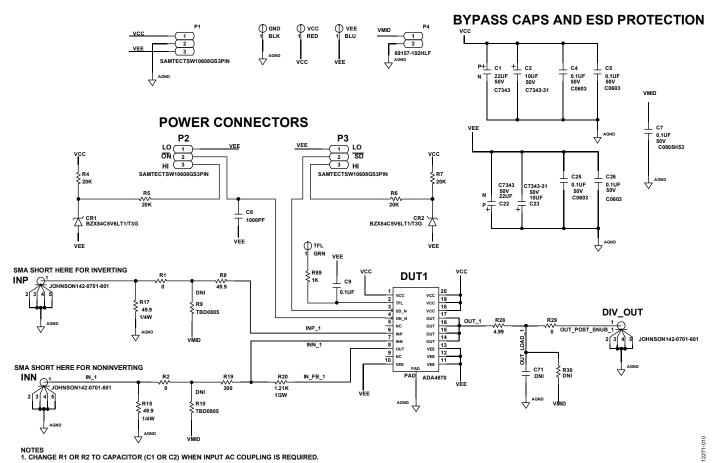

Figure 10 shows the evaluation board schematic for the factory default settings when the board is shipped.

The evaluation board uses edge-mount SMA connectors on the inputs and outputs for easy interfacing to signal sources and test equipment. When evaluating high voltage output signals using standard 50  $\Omega$  test equipment, R29 can be replaced with a 2.45 k $\Omega$  resistor that provides a signal division of 49.6 at the DIV\_OUT SMA connector. The board can accommodate a capacitor load (C71) referenced to GND, and/or a power resistor in the TO-220 package (R30) referenced to VMID.

When using input signals of 5 V and lower, the board is equipped with 49.9  $\Omega$ , 0.25 W resistors at R17 and R18 that are capable of handling the power when using the factory default settings. The factory default configuration provides for operation on dual symmetrical supplies in noninverting and inverting gains of +4.5 V/V, and -4.0 V/V respectively. For single-supply and asymmetrical supply operation, see the Asymmetrical Supplies and Mid Supply Bias (VMID) section and Table 1 for guidance on configuring the input terminations and supply settings.

# SYMMETRICAL SUPPLIES AND DC-COUPLED INPUTS

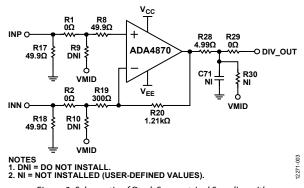

Figure 3 shows the noninverting or inverting configuration schematic when using dual, symmetrical supplies. When using the factory default settings with noninverting input, the ground reference is established through the 49.9  $\Omega$  termination resistors (R17 and R18), and the gain can be calculated using R20/(R19 + R18). The gain is +4.5 V/V for the factory default settings. When using the factory default settings with inverting input, the gain can be calculated using R20/R19. The gain is -4.0 V/V for the factory default settings. In dual-supply operation when installing R30 in either inverting or noninverting applications, position the jumper at P4 to short VMID to GND.

Figure 3. Schematic of Dual, Symmetrical Supplies with Noninverting or Inverting Input

# ASYMMETRICAL SUPPLIES AND MID SUPPLY BIAS (VMID)

Figure 4 and Figure 5 show schematics when using a single supply with ac-coupled input.

The ADA4870 must be referenced to a dc operating point. When using a single supply or asymmetrical dual supplies, apply the appropriate reference voltage to the VMID pin of P4 using a low impedance source, such as a dc supply. The recommended VMID reference voltage is  $V_{\text{EE}} + (V_{\text{CC}} - V_{\text{EE}})/2$ .

When ac coupling into the noninverting input (INP), the dc operating point of the amplifier can be established by installing a resistor at R9 connected to VMID and replacing R1 with an ac coupling capacitor (C1), as shown in Figure 4. The ac coupling capacitor (C1) combined with the VMID bias resistor (R9) form a high-pass filter with the cutoff frequency at  $1/(2\times\pi\times R9\times C1)$ . The value of the ac coupling capacitor (C1) can be calculated based on the desired cutoff frequency.

When ac coupling into the inverting input (INN), the dc operating point of the amplifier can be established by shorting R9 to VMID. Do not install R1.

Figure 4. Schematic of Single Supply with Noninverting Input

Figure 5. Schematic of Single Supply with Inverting Input

**Table 1. Configuration of Input Components**

| J I I I             |               |          |            |               |               |                        |                        |                   |

|---------------------|---------------|----------|------------|---------------|---------------|------------------------|------------------------|-------------------|

| Supply <sup>1</sup> | Configuration | Coupling | Gain (V/V) | R9 (Ω)        | R10 (Ω)       | R1 (Ω)                 | R2 (Ω)                 | P4 (VMID)         |

| Dual                | Noninverting  | DC       | +4.5       | Do not insert | Do not insert | 0                      | 0                      | Open <sup>2</sup> |

| Dual                | Inverting     | DC       | -4.0       | Do not insert | Do not insert | 0                      | 0                      | Open <sup>2</sup> |

| Single              | Noninverting  | AC       | +5.0       | 1,000         | 0             | Capacitor <sup>3</sup> | Do not insert          | DC voltage supply |

| Single              | Inverting     | AC       | -4.0       | 0             | Do not insert | Do not insert          | Capacitor <sup>3</sup> | DC voltage supply |

<sup>&</sup>lt;sup>1</sup> Dual means symmetrical supplies; single means any nonsymmetrical supplies.

<sup>&</sup>lt;sup>2</sup> If R30 is installed, short VMID to GND.

<sup>&</sup>lt;sup>3</sup> When input ac coupling is required, replace the dc coupling resister with an ac coupling capacitor.

### **ON, INITIAL POWER-UP, AND SHORT CIRCUIT**

The board is shipped with the  $\overline{ON}$  pin pulled low to  $V_{EE}$  at P1 to ensure that the amplifier is enabled. Subsequently, floating the  $\overline{ON}$  pin enables the short-circuit protection feature while the amplifier remains on. While  $\overline{ON}$  is held low, the short-circuit protection feature is disabled.

The  $\overline{ON}$  pin turns on the amplifier after initial power-up and after a short-circuit event. The pin is referenced to the negative supply (V<sub>EE</sub>).

When a short-circuit condition is detected, the amplifier is disabled, the supply current drops to approximately 5 mA, and the TFL pin outputs a dc voltage of approximately 300 mV above  $V_{\rm EE}$ . To turn the amplifier back on after a short-circuit event, follow the previously described sequence for initial power-up.

Pulling the  $\overline{ON}$  pin high disables the amplifier and causes the supply current to drop to approximately 5 mA, as if a short-circuit condition had been detected. Pin 3 of P2 uses a 5 V Zener diode (CR1) to set the high level at 5 V above V<sub>EE</sub>.

The impedance at  $\overline{ON}$  is approximately 20 k $\Omega$ . The  $\overline{ON}$  pin is decoupled to  $V_{EE}$  via C8 to shunt noise away from  $\overline{ON}$  and to help avoid false triggers.

### SHUTDOWN (SD)

$\overline{D}$  pin to the HI position,  $V_{EE}$  + 5.2 V. Pulling the  $\overline{SD}$  pin low to  $V_{EE}$  places the amplifier in a low power shutdown state, reducing the quiescent current to approximately 750  $\mu A.$  The  $\overline{SD}$  pin must be pulled low to a maximum of  $V_{EE}$  + 0.9 V for shutdown, or pulled high to a minimum of  $V_{EE}$  + 1.1 V to enable

the amplifier. Do not float the pin. When turning the amplifier back on from the shutdown state, pull the  $\overline{SD}$  pin high and then pull the  $\overline{ON}$  pin low. Following this sequence is required to turn on the ADA4870. To enable the short-circuit protection, the  $\overline{ON}$  pin must float following the turn on sequence.

### THERMAL MONITOR/SHORT-CIRCUIT FLAG (TFL)

The TFL pin can be used to monitor relative changes in die temperature and to detect a short-circuit condition. During normal operation, the TFL pin outputs a dc voltage that is approximately 1.7 V (typical) above V<sub>EE</sub> and is related to the die temperature. The TFL voltage changes at approximately -3 mV/°C. When the die temperature exceeds approximately 140°C, the amplifier switches to an off state, dropping the supply current to approximately 5 mA while TFL continues to report a voltage indicative of the die temperature. When the die temperature returns to an acceptable level, the amplifier automatically resumes normal operation.

### THERMAL DESIGN AND HEAT SINK SELECTION

In some applications, the ADA4870 may be required to dissipate as much as 10 W at elevated ambient temperatures of up to +85°C. The evaluation board provides robust thermal management under these conditions.

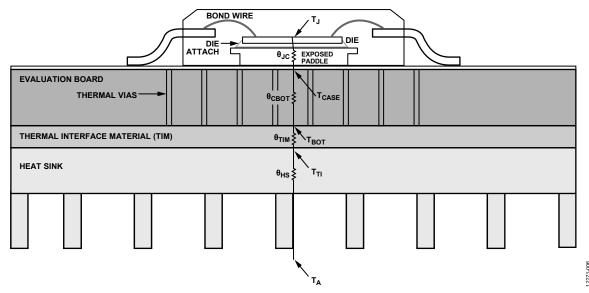

The top of the board has an exposed copper area to which the ADA4870 PSOP package must be soldered. The exposed copper area allocated to the attachment of the PSOP slug is connected to the exposed copper ground plane on the bottom by an array of 136 thermal vias. A single internal ground layer (Layer 2) is also attached. Figure 6 shows a model of the ADA4870 package mounted to the evaluation board with an applied heat sink.

Figure 6. Thermal Model for ADA4870 with Heat Sink

When necessary, a heat sink can be mounted to the bottom exposed copper using the mounting holes and an applied thermal interface material (TIM), such as the GC Electronics 10-8109. Refer to the manufacturer guidelines when applying the TIM; the TIM thermal resistance ( $\theta_{\text{TIM}}$ ) must be no more than 0.3°C/W. See Figure 7 for the dimensions of the heat sink and mounting hole locations. The approximate thermal resistance of the heat sink can be calculated from Equation 1, where  $\theta_{\text{JC}}$  equals 1.1°C/W and  $\theta_{\text{CBOT}}$  is approximately equal to 1.0°C/W. A heat sink having a thermal resistance of 4.2°C/W allows 10 W of power dissipation at an ambient temperature of 85°C.

$$\theta_{HS} = \left(\frac{T_J - T_A}{P_{DISS}}\right) - (\theta_{JC} + \theta_{CBOT} + \theta_{TIM})$$

(1)

where.

$T_I$  is the junction temperature.

$T_A$  is the ambient temperature.

$P_{DISS}$  is the chip power dissipation.

$\theta_{JC}$  is the chip thermal resistance.

$\theta_{CBOT}$  is the thermal resistance of the chip solder material and the PCB.

$\theta_{TIM}$  is the TIM thermal resistance.

Figure 7. Dimensions of the Heat Sink and Mounting Holes

#### THERMAL PERFORMANCE

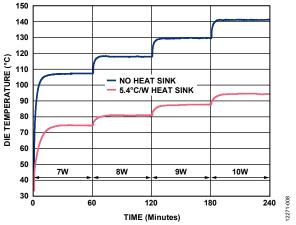

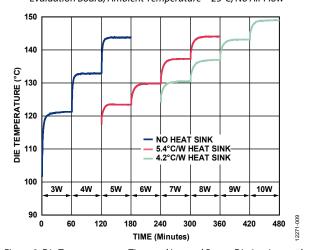

Figure 8 and Figure 9 show the die temperature vs. time while the internal power dissipation is increased over several hours. The ambient environment for Figure 8 is 25°C in still air; for Figure 9, the ambient environment is 85°C in still air. Figure 8 shows the die temperature in two conditions: one without a heat sink and the other with a heat sink rated at 5.4°C/W. Figure 9 shows the die temperature in three conditions: one without a heat sink, the second with a heat sink rated at 5.4°C/W, and the third with a heat sink rated at 4.2 °C/W. For both Figure 8 and Figure 9, the board is positioned with the bottom side or heat sink facing up to facilitate natural convection. Using ac power dissipation and/or forced convection result in lower temperature.

Figure 8. Die Temperature vs. Time and Internal Power Dissipation on the Evaluation Board, Ambient Temperature = 25°C, No Air Flow

Figure 9. Die Temperature vs. Time and Internal Power Dissipation on the Evaluation Board, Ambient Temperature = 85°C, No Air Flow

2271

### **EVALUATION BOARD SCHEMATIC**

Figure 10. Evaluation Board Schematic

# **BILL OF MATERIALS**

Table 2.

|      | 04  | Reference            | D                                                | V-I            | Manufacture (Dart Na               |

|------|-----|----------------------|--------------------------------------------------|----------------|------------------------------------|

| Item | Qty | Designator           | Description                                      | Value          | Manufacturer/Part No.              |

| 1    | 1   | Not applicable       | ADA4870 evaluation board                         | Not applicable | Analog Devices/ADA4870ARR-EBZ      |

| 2    | 1   | DUT1                 | ADA4870                                          | Not applicable | Analog Devices/ADA4870             |

| 3    | 2   | C1 ,C22              | Capacitor, tantalum, 7343                        | 22 μF          | AVX/TAJD226K050R                   |

| 4    | 2   | C2, C23              | Capacitor, tantalum, 7343                        | 10 μF          | AVX/TAJD106M050RNJ                 |

| 5    | 5   | C4, C5, C9, C25, C26 | Capacitor, ceramic, X7R, 0603                    | 0.1 μF         | AVX/06035C104KAT2A                 |

| 6    | 1   | C7                   | Capacitor, ceramic, X7R,0805, 50 V               | 0.1 μF         | Murata/GRM21BR71H104KA01L          |

| 7    | 1   | C71                  | Capacitor, ceramic, COG, 0603, 50 V              | Not installed  | Murata/GRM1885C1H301JA01D          |

| 8    | 1   | C8                   | Capacitor ceramic, X7R, 0603, 50 V               | 1000 pF        | AVX/06035C102KAT2A                 |

| 9    | 2   | CR1, CR2             | Diode, Zener, SOT-23                             | 5.6 V          | ON Semiconductor/BZX84C5V6LT1/T3G  |

| 10   | 3   | INP, INN, DIV_OUT    | Connector, SMA end launch                        | Not applicable | Johnson/142-0701-801               |

| 11   | 1   | GND                  | Connector, test point                            | Black          | Components Corporation/TP104-01-00 |

| 12   | 3   | P1, P2, P3           | Connector, PCB, berg, header, straight, male, 3P | Not applicable | Samtec/TSW-103-08-G-S              |

| 13   | 1   | P4                   | Connector, PCB, berg, jumper, straight, male, 2P | Not applicable | FCI/69157-102HLF                   |

| 14   | 2   | R1,R2                | Resistor, 0603, jumper                           | 0Ω             | Panasonic/EERJ-3GEY0R00V           |

| 15   | 2   | R9, R10              | Resistor, 0805                                   | Not installed  |                                    |

| 16   | 2   | R17, R18             | Resister, 1206, 1%                               | 49.9 Ω         | Panasonic/ERJ-8ENF49R9V            |

| 17   | 1   | R19                  | Resistor, 1206, 1%                               | 300 Ω          | Vishay Dale/CRCW1206300RFKEA       |

| 18   | 1   | R20                  | Resistor, 2010, 1%                               | 1.21 kΩ        | Panasonic/ERJ-12SF1211U            |

| 19   | 1   | R28                  | Resistor, 2512, 1%                               | 4.99 Ω         | Vishay Dale/CRCW25124R99FKEG       |

| 20   | 1   | R29                  | Resistor, 1206, jumper                           | 0Ω             | Vishay Dale/CRCW12060000Z0EA       |

| 21   | 1   | R30                  | Resistor, TO-220                                 | Not installed  | ,                                  |

| 22   | 4   | R4, R5, R6, R7       | Resistor, 0603, 1%                               | 20 kΩ          | Panasonic/ERJ-3EKF2002V            |

| 23   | 1   | R8                   | Resistor, 0603, 1%                               | 49.9 Ω         | Panasonic/ERJ-3EKF49R9V            |

| 24   | 1   | R89                  | Resistor, 0603, 1%                               | 1 kΩ           | Panasonic/ERJ-3EKF1001V            |

| 25   | 1   | TFL                  | Connector, test point                            | Green          | Components Corporation/TP104-01-05 |

| 26   | 1   | VCC                  | Connector, test point                            | Red            | Components Corporation/TP104-01-02 |

| 27   | 1   | VEE                  | Connector, test point                            | Blue           | Components Corporation/TP104-01-06 |

| 28   | 2   | Jumper               | Jumper socket for P2 and P3                      | Not applicable | FCI/65474-001LF                    |

### **NOTES**

**ESD Caution**

**ESD** (**electrostatic discharge**) **sensitive device**. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer; all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the RoHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer, Customer agrees to return to ADI the Evaluation Board at that time, LIMITATION OF LIABILITY, THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL, SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2014–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

UG12271-0-6/16(A)

www.analog.com